計算機的組成原理是現代信息技術的基礎,其中主存儲器(Main Memory)作為計算機硬件系統的核心組件之一,承擔著程序與數據的臨時存儲任務。它與中央處理器(CPU)直接交互,是影響計算機整體性能的關鍵因素。與此在當今網絡化的計算環境中,主存儲器也與各類網絡設備緊密協作,共同構成了高效、可靠的信息處理與傳輸體系。

一、主存儲器的硬件組成

主存儲器,通常指隨機存取存儲器(RAM),其硬件結構主要由以下幾個部分構成:

- 存儲體(Memory Bank/Cell Array):這是存儲器的核心,由大量基本存儲單元(Memory Cell)構成。每個存儲單元通常由電容和晶體管組成(如在動態隨機存取存儲器DRAM中),能夠存儲一個二進制位(bit)。這些單元按矩陣形式排列,通過行地址和列地址進行尋址。

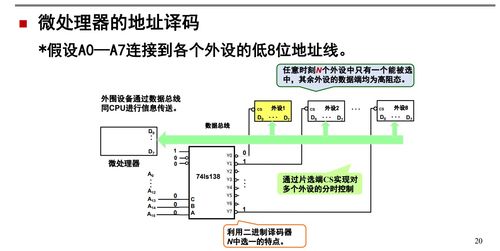

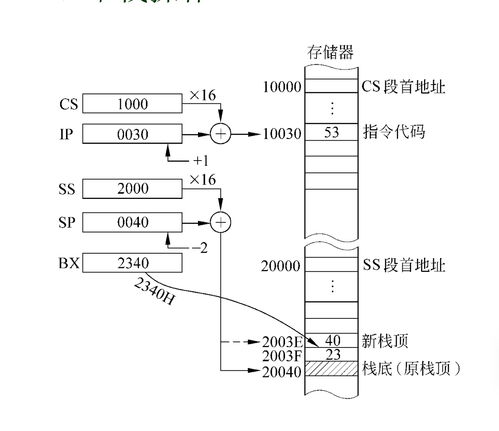

- 地址寄存器(Address Register, MAR)和地址譯碼器(Address Decoder):CPU或內存控制器將需要訪問的存儲單元地址送入地址寄存器。地址譯碼器則將該地址轉換為對應存儲單元的行選和列選信號,從而選中特定的存儲單元。

- 數據寄存器(Data Register, MDR)/ 讀寫驅動器(Read/Write Drivers):在讀取操作時,從被選中的存儲單元中讀出的微弱電信號經過放大后,暫存于數據寄存器,準備傳送給CPU。在寫入操作時,CPU要寫入的數據首先送入數據寄存器,再由讀寫驅動器將其轉換為足夠的電平信號,寫入到指定的存儲單元中。

- 時序控制電路(Timing and Control Circuitry):負責產生和協調存儲器內部各項操作(如預充電、行激活、列選通、讀寫等)所需的控制信號和時序,確保讀寫操作準確無誤地按照規定的時鐘周期完成。它接收來自內存控制器的命令(如讀、寫、刷新)。

- 刷新電路(Refresh Circuitry):對于DRAM,因其存儲電容上的電荷會隨時間泄漏,必須定期(通常每64ms)對所有存儲單元進行刷新以保持數據。刷新電路負責生成刷新地址和控制信號,在不干擾正常讀寫操作的情況下完成刷新任務。

- 內存控制器(Memory Controller):通常位于計算機主板上的北橋芯片組或集成于CPU內部。它是CPU與主存之間的接口,負責管理內存的地址映射、訪問時序、刷新調度以及錯誤校驗(如ECC)等高級功能。

二、主存儲器與網絡設備的硬件關聯

在聯網的計算機系統中,主存儲器不僅服務于本地CPU的計算任務,也與網絡設備的協同工作息息相關。網絡設備(如網卡NIC、路由器、交換機等)與主存的交互主要通過以下方式實現:

- 直接內存訪問(DMA):這是關鍵機制。網絡接口卡(NIC)通常具備DMA控制器。當有網絡數據包到達或需要發送時,NIC的DMA控制器可以在不占用CPU資源的情況下,直接與主存儲器進行數據交換。它將接收到的數據包直接寫入主存中操作系統預先分配的緩沖區,或從主存的發送緩沖區直接讀取數據包進行發送。這極大地減輕了CPU的負擔,提高了網絡吞吐率。

- 共享內存區域:操作系統會為核心網絡協議棧(如TCP/IP協議棧)和網卡驅動程序在主存中劃分專用的數據緩沖區(發送/接收緩沖區)。這些區域成為CPU(執行協議處理)和網絡設備硬件之間共享的數據交換區。

- 對網絡設備性能的影響:主存儲器的性能(如帶寬、延遲)直接影響網絡數據處理的速度。高速的DDR4/DDR5內存能夠更快地為網卡提供發送數據或接納接收數據,減少數據在內存總線上的排隊延遲,從而支持更高的網絡速率(如萬兆以太網)。

- 在網絡設備內部的角色:高端路由器、交換機等網絡設備本身也包含類似計算機的硬件體系,擁有自己的主存儲器(通常是高性能的SRAM或DRAM)。這些內存用于存儲轉發表(FIB)、路由表、數據包緩沖區、隊列管理信息等,是實現高速數據包轉發和復雜網絡策略的核心硬件資源。其容量和速度直接決定了設備的轉發能力和并發連接數。

結論

計算機的主存儲器是一個精密的硬件系統,由存儲體、譯碼電路、控制電路等部件協同工作。在聯網環境中,通過DMA等機制,主存儲器與網絡設備硬件形成了高效的數據通道,使得數據能在計算核心與網絡之間流暢傳輸。理解主存儲器的硬件組成及其與網絡設備的交互,對于設計高性能計算系統、優化網絡應用以及進行底層系統開發都具有重要意義。從單機到網絡,主存儲器始終是信息存儲與流動的關鍵樞紐。